# PWM ボード仕様書

- (B 判)2007/08/01 阿部

- (D 判)2007/11/12 阿部 アドレスマップ変更

- (E判)2007/11/30 阿部 アドレスマップの CARRY レジスタ幅修正(11→12bit)

- (F判)2008/03/26 阿部 図版を PK06-4003E から PZ06-5058F に変更

- (G 判)2010/11/29 佐藤 表 13 の Pin 番号を変更(23,24,25→13,14,15, 13,14,15→23,24,25)

適用

本仕様書は、PK06-4003 PWM ボードについての仕様をまとめる。

#### 1. 機能ブロック図および機能概要

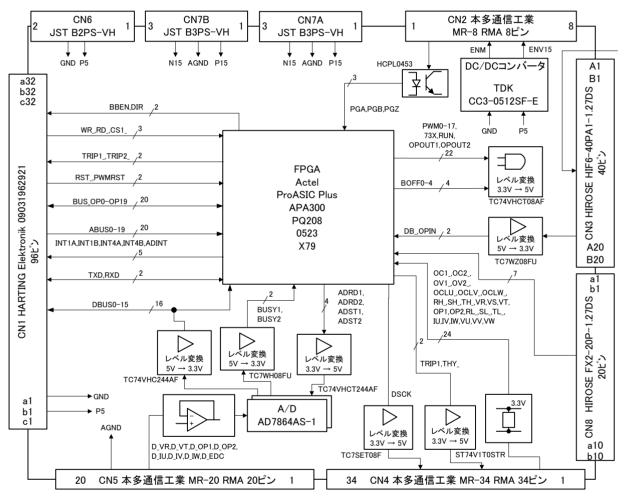

図1機能ブロック図

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG.

Memo:

1/23

(F判)2008/03/26 阿部 図版をPK06-4003EからPZ06-5058Fに変更

(G判)2010/11/29 佐藤 表 13の Pin 番号を変更

## 表 1 機能概要

| 機能             | 部品名     | 内容                                            |

|----------------|---------|-----------------------------------------------|

|                |         | (1) PWM 信号 18 本(H アクティブ,5V)出力可                |

|                |         | (2) 初期充電抵抗用信 <del>号</del> 出力可                 |

| <br>  PWM 出力   | CN3     | (3) DB 用信号出力可                                 |

|                | CIVO    | (4) オプション出力1本                                 |

|                |         | (5) オプション入力1本                                 |

|                |         | (6) 5V 電源供給可                                  |

|                |         | (1) 検出ボードの電圧, 電流検出値を入力。出力電流(U,V,W 相), 直       |

|                |         | 流中間電圧(Edc),入力電圧(R,T 相),予備 2 チャンネル検出可能         |

|                |         | (2) アナログ入力±10V                                |

| A/D            | CN5     | (3) 変換値は符号付 12 ビット                            |

|                |         | (4) AD コンバータ2個実装。1個あたり 4ch 同時変換。              |

|                |         | (5)変換時間 1ch あたり 1.65 μ s(4ch 同時変換時 6.825 μ s) |

|                |         | (6) アナログ入力はボルテージフォロワあり                        |

| <br>  ディジタル入出力 | CN4     | (1) 検出ボードの過電圧, 過電流信号入力。                       |

| ノイングル人田力       | CIV4    | (2) マトコン用信号(極性信号, 最大相等)入力。                    |

| 電源             | CN6,CN7 | +5V,±15V                                      |

| 电师             | ONO,ON7 | ※必ず両電源を投入のこと。但し,+5V は共通バスからも供給可。              |

|                |         | (1) FRENIC-VG7 シリーズ専用モータ標準 PG インターフェース準拠。     |

| PG インターフェース    | CN2     | (2) A,B,Z 相の 3 相パルス入力, 3 相パルス出力。              |

|                |         | (3) フォトカプラによる入出力絶縁。                           |

|                |         | (4) PG の駆動電源(15V)は本基板で生成。                     |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>2/23</sub>

DWG. NO.

Memo:

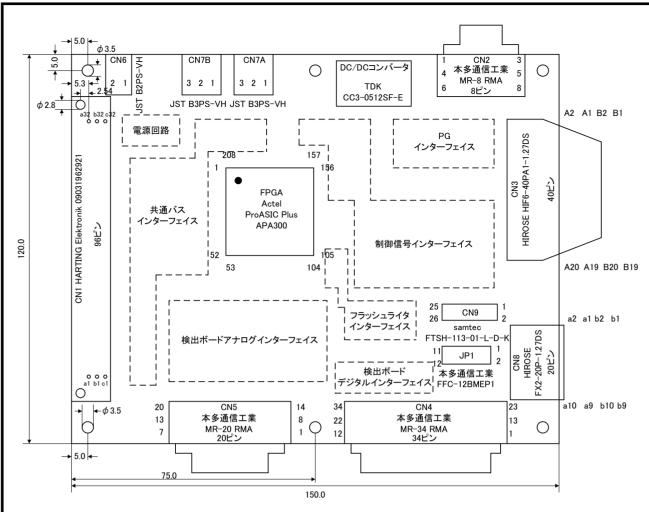

図 2 レイアウト図

**Power Electronics Lab.** Nagaoka University of Tech.

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

3/23

(F判)2008/03/26 阿部 図版をPK06-4003E から PZ06-5058F に変更 (G判)2010/11/29 佐藤 表 13 の Pin 番号を変更

### 2.2 アドレスマップ

- (1) ABUS16-19 はベースアドレスとする。 PWM ボードのベースアドレスは 2 とする。

- (2) Read/Write は CPU 側が基準

- (3) アドレスは最下位を A0 としている。

|                | 1           | 1           | L                    | T                             |

|----------------|-------------|-------------|----------------------|-------------------------------|

| アドレス           | レジスタ        | R/W         | 機能                   | 備考                            |

| 0x22000        | ADBUSY1     | R           | AD コンバータ BUSY 信号 1   | AD 変換処理中は 1                   |

| 0×22008        |             | R           | <br>  AD 変換値リード信号 1  | 読み込みイネーブルでADコンバータ1            |

| 0x22008        |             | , r         | AD 多換値リード信号          | が AD データ出力                    |

| 0x22010        | ADBUSY      | R           | AD コンバータ BUSY 信号 2   | AD 変換処理中は 1                   |

| 0x22018        |             | R           | <br>  AD 変換値リード信号 2  | 読み込みイネーブルでADコンバータ2            |

| 0XZZ010        |             | K           | AD 多換値が一下信与 2        | が AD データ出力                    |

| 0x21000        | DUTYREF_U1  | w           | <br>  U 相デューティ指令 1   | 12 ビット(0~4096)初期値 0           |

| 0X21000        |             | VV          | 0 個 7 立一 7 4 個 节     | 出力先 Up:PWM5 , Un:PWM2         |

| 0x21010        | DUTYREF_V1  | w           | <br>  V相デューティ指令 1    | 12 ビット(0~4096)初期値 0           |

| 0.21010        |             | VV          | V1日 / ユ              | 出力先 Up:PWM4 , Vn:PWM1         |

| 0x21020        | DUTYREF_W1  | w           | <br>  W 相デューティ指令 1   | 12 ビット(0~4096)初期値 0           |

| 0.21020        |             | **          | W16/1 /116   1       | 出力先 Wp:PWM3, Wn:PWM0          |

| 0x21100        | DUTYREF_U2  | w           | <br>  U 相デューティ指令 2   | 12 ビット(0~4096)初期値 0           |

| 0,21100        |             | **          | 01872 7118 132       | 出力先 Up:PWM11, Un:PWM8         |

| 0x21110        | DUTYREF_V2  | w           | <br>  ∨相デューティ指令 2    | 12 ビット(0~4096)初期値 0           |

| 0,21110        |             | **          | V16 / ユ              | 出力先 Up:PWM10, Vn:PWM7         |

| 0x21120        | DUTYREF_W2  | w           | <br>  W 相デューティ指令 2   | 12 ビット(0~4096)初期値 0           |

| 0,21120        |             | **          | W1672 7116 122       | 出力先 Wp:PWM9, Wn:PWM6          |

| 0x21200        | DUTYREF_U3  | w           | <br>  U 相デューティ指令 3   | 12 ビット(0~4096)初期値 0           |

| 0,21200        |             | **          | 0 16 7 2 7 7 16 13 0 | 出力先 Up:PWM17, Un:PWM14        |

| 0x21210        | DUTYREF_V3  | w           | <br>  V相デューティ指令 3    | 12 ビット(0~4096)初期値 0           |

| OXZTZTO        |             | "           | V107                 | 出力先 Up:PWM16, Vn:PWM13        |

| 0x21220        | DUTYREF_W3  | w           | <br>  W 相デューティ指令 3   | 12 ビット(0~4096)初期値 0           |

| OXZTZZO        |             | "           | W117 2 7418 13 0     | 出力先 Wp:PWM15, Wn:PWM12        |

| 0x23000        | D_TIME      | W           | デットタイム               | 8 ビット(0~256)初期値 120(3 μ s)    |

| 0x24000        | REG_TRIP_WT | W           | ソフトトリップ              | 1 でゲートオン,0 で遮断                |

| 0x25000 REG_TF | REG_TRIP_RD | G_TRIP_RD R | トリップ読み込み             | 5 ビット。上位ビットから                 |

| UAZ3000        |             | 11          |                      | WDT,OV2,OV1,OC2,OC1(アクティブ H)  |

| 0x26000        | GATEON      | W           | ゲートオン許可              | 1 でゲートオン,0 で遮断                |

| 0x28000        | CRYPK       | W           | キャリアカウント値設定          | 12 ビット(0~4096)初期値 2000(10kHz) |

| 0x27000        | MCON        | W           | MCドライバ用信号            | 1でTHY_が Low                   |

|                | _           | ·           | ı                    |                               |

※ CPU に C6713 使用時には上位アドレス B00 を追加のこと(例:0xB0010000)

#### 2. 3 詳細仕様

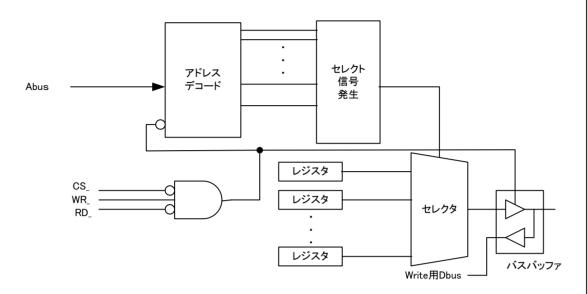

2. 3. 1 アドレスデコーダ(モジュール名 REGCTL)

#### 1機能

- (1) アドレスバス 20bit, ただし, A16-A19 はベースアドレス, A0,A1 は常にゼロ(64bit アクセス)

- (2) クロック 40MHz

- (3) 内部レジスタは REGCTL に持つ。

- (4) AD コンバータ用制御信号生成

| Power Electronics Lab.      |       | DATE       | NAME | Ö     |            |      |

|-----------------------------|-------|------------|------|-------|------------|------|

| Nagaoka University of Tech. | DRAWN | 11/29/2010 | 佐藤   | VG. N | PZ06-5058G | 5/22 |

| ragacka criivereky cr reen. | CHECK |            |      | △     |            | 3/23 |

(F判)2008/03/26 阿部 図版をPK06-4003EからPZ06-5058Fに変更 (G判)2010/11/29 佐藤 表 13の Pin 番号を変更

Memo:

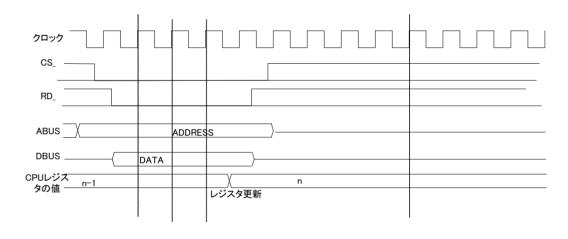

#### 2読み出し時

注意事項:CPU を基準とする

- (1) RDBUS の立下りより 3 クロック以内に、FPGA 内のレジスタの値を Dbus に出力する。よって、CPU 側の wait 時間は 100ns 以上(3 クロック+1 クロックマージン)に設定すること。

- (2) 3 クロック後データが確定していればいいので、同期化は不要。

図4 読み出し時アドレスデコーダブロック図

図 5 読み出し時アドレスデコードタイミング

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

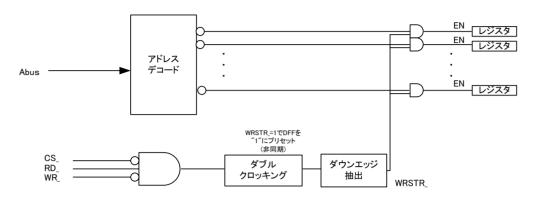

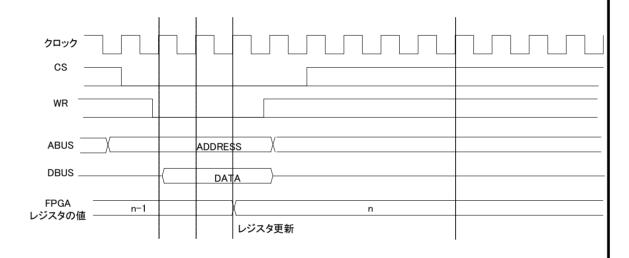

### 3書き込み時

注意事項:CPU を基準とする

- (1) WR\_の立下りより 3 クロックで DBUS の内容を FPGA 内レジスタに書き込む。 したがって、CPU 側の Wait 時間は 100ns 以上(3 クロック+1クロックマージン)にすること。

- (2) WR\_が立ちあがったとき、ダブルクロッキング部のすべての DFF をただちに1にプリセットする。クロックとは非同期。

図6 書き込み時アドレスデコーダブロック図

図7 書き込み時アドレスデコードタイミング

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

#### 4 レジスタフォーマット

<REG ADBUSY1>:AD コンバータ 1BUSY 信号

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------|

| 機能  | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | BUSY1 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | 0     |

<REG ADBUSY2>:AD コンバータ 2BUSY 信号

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------|

| 機能  | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | BUSY2 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | 0     |

<DUTYREF U>:U 相デューティ指令

| ピット | 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 機能  | -  | -  | -  | -  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 初期値 | -  | -  | -  | -  | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  |

<DUTYREF\_V>:V 相デューティ指令

| ピット | 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 機能  | -  | -  | -  | -  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 初期値 | -  | -  | -  | -  | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  |

<DUTYREF\_W>:W 相デューティ指令

| ピット | 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 機能  | -  | -  | -  | -  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 初期値 | -  | -  | -  | -  | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  |

<D\_TIME>:デットタイム時間

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| 機能  | -  | -  | -  | -  | -  | -  | - | - | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

<CRYPK>:キャリアピーク

| ピット | 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 機能  | -  | -  | -  | -  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 初期値 | -  | -  | -  | -  | 0   | 1   | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  |

<REG\_TRIP\_RD>:ソフトトリップ

|     |    |    |    |    | -  |    |   |   |   |   |   |   |   |   |   |    |

|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| 機能  | -  | -  | ı  | -  | -  | -  | - | ı | - | - | • | ı | - | - | - | D0 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | 0  |

**Power Electronics Lab.** Nagaoka University of Tech.

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>8/23</sub>

(F判)2008/03/26 阿部 図版をPK06-4003EからPZ06-5058Fに変更

(G判)2010/11/29 佐藤 表 13の Pin 番号を変更

#### <REG\_TRIP\_WT>:トリップ読み込み

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4      | 3   | 2   | 1   | 0   |

|-----|----|----|----|----|----|----|---|---|---|---|---|--------|-----|-----|-----|-----|

| 機能  | -  | -  | -  | -  | -  | -  | - | - | - | - | - | TRIP1_ | OV2 | OV1 | OC2 | OC1 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | - | - | - | 0      | 0   | 0   | 0   | 0   |

#### <GATEON>:ゲートオン許可

| ピット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 機能  | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | D0 |

| 初期値 | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | 1  |

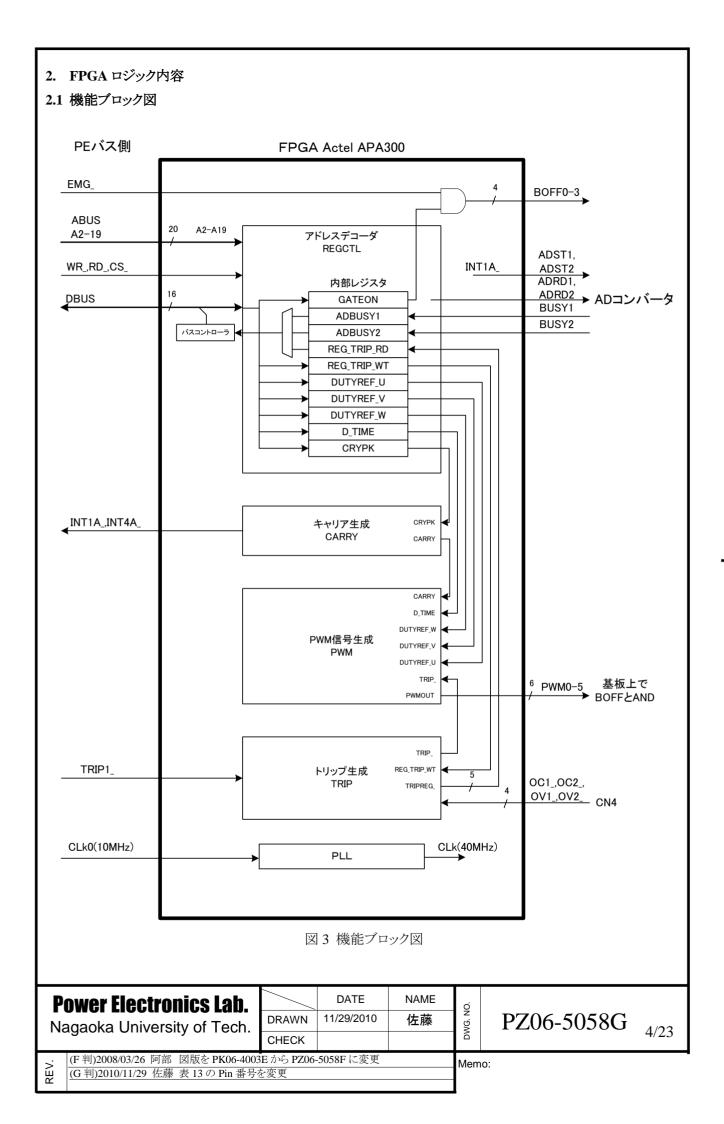

## 2. 3. 2 キャリア生成(モジュール名: CARRY)

- (1)三角波キャリア生成

- (2)キャリアピーク値はレジスタ CRYPK で設定(0~2048)

- (3)キャリアの山で割込み信号 INT1A\_,INT4A\_(INT1A\_の 8 倍周期)出力

#### 2. 3. 3 PWM 生成(モジュール名: PWM)

- (1)PWM 信号を出力。三角波比較。

- (2)U,V,W 相指令はレジスタ DUTYREF\_U, DUTYREF\_V, DUTYREF\_W で設定(0~2048)

- (3)デットタイムはレジスタ D\_TIME で設定(0~256=0~6.4  $\mu$  s)

- (4)トリップ信号とAND してからPWM信号出力。よって、トリップ時にはPWM指令は0。

#### 2. 3. 4 トリップ生成(モジュール名:TRIP)

- (1) ディジタル入力 CN 4の OC1\_,OC2\_,OV1\_,OV2\_,及び PE バスの TRIP1\_, ソフトトリップ用レジスタ REG\_TRIP\_RD のいずれかがアクティブの時,トリップ信号出力

- (2) 各信号はアクティブになった時ラッチ。

- (3) OC1 ,OC2 ,OV1 ,OV2 ,REG TRIP RD のラッチ解除は PE バスの PWMRST で, TRIP1 のラッチ解除 はPEバスのRST\_で行う。

- (4) トリップ情報はレジスタ REG\_TRIP\_WT に格納。上位ビットから TRIP1\_,OV2,OV1,OC2,OC1。アクティブ時 に10

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>9/23</sub>

DWG. NO.

Memo:

## 3. コネクタマップ

## 3.1CN1 共通バスインターフェース

(1)共通バスインターフェースに用いるコネクタ CN1 は HARTING 09031962921(ライトアングル 96 ピン)

表5 CN1 共通バスコネクタマップ

| A列 | 機能             | B列 | 機能              | C 列 | 機能               |

|----|----------------|----|-----------------|-----|------------------|

| 1  | D4             | 1  | PWMRST_(NC)     | 1   | D5               |

| 2  | D3             | 2  | RD_(NC)         | 2   | D6               |

| 3  | D2             | 3  | TRIP2_(ACFAIL_) | 3   | D7               |

| 4  | D1             | 4  | +5V (NC)        | 4   | D8               |

| 5  | D0             | 5  | GND             | 5   | D9               |

| 6  | INT1A_(INT4_)  | 6  | +5V (NC)        | 6   | D10              |

| 7  | INT1B_(INT5_)  | 7  | +5V (NC)        | 7   | D11              |

| 8  | INT4A_(INT6_)  | 8  | GND (NC)        | 8   | D12              |

| 9  | GND            | 9  | +5V (NC)        | 9   | GND              |

| 10 | INT4B_(SYSCLK) | 10 | +5V (NC)        | 10  | TRIP1_(SYSFAIL_) |

| 11 | GND            | 11 | EMG_(NC)        | 11  | D13              |

| 12 | RXD (MODE)     | 12 | GND             | 12  | RST_(RESTOUT_)   |

| 13 | CS1_(CEXTCS_)  | 13 | OP16 (BA3)      | 13  | D14              |

| 14 | WR_(R/W_)      | 14 | OP17(BA2)       | 14  | D15              |

| 15 | GND            | 15 | OP18(BA1)       | 15  | OP0 (D16)        |

| 16 | RDY_(Res.)     | 16 | OP19(BA0)       | 16  | OP1 (D17)        |

| 17 | GND            | 17 | A21             | 17  | OP2 (D18)        |

| 18 | BBEN_(IOCS_)   | 18 | A20             | 18  | OP3 (D19)        |

| 19 | GND            | 19 | A19             | 19  | OP4 (D20)        |

| 20 | TXD (Res.)     | 20 | GND             | 20  | OP5 (D21)        |

| 21 | ADST_(Res.)    | 21 | A18             | 21  | OP6 (D22)        |

| 22 | DIR (Res.)     | 22 | A9              | 22  | OP7 (D23)        |

| 23 | A17            | 23 | GND             | 23  | OP8 (D24)        |

| 24 | A16            | 24 | A8              | 24  | OP9 (D25)        |

| 25 | A15            | 25 | A7              | 25  | OP10(D26)        |

| 26 | A14            | 26 | A6              | 26  | OP11 (D27)       |

| 27 | A13            | 27 | A5              | 27  | OP12(D28)        |

| 28 | A12            | 28 | A4              | 28  | OP13 (D29)       |

| 29 | A11            | 29 | A3              | 29  | OP14(D30)        |

| 30 | A10            | 30 | A2              | 30  | OP15(D31)        |

| 31 | +5V (NC)       | 31 | GND (NC)        | 31  | +5V (NC)         |

| 32 | +5V            | 32 | +5V             | 32  | +5V              |

| Power Electronics Lab.      |       | D    |

|-----------------------------|-------|------|

| Nagaoka University of Tech. | DRAWN | 11/2 |

| rtagacha chirolony chirochi | CHECK |      |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

10/23

(F判)2008/03/26 阿部 図版をPK06-4003EからPZ06-5058Fに変更

(G判)2010/11/29 佐藤 表 13 の Pin 番号を変更

## (2)各信号の内容を表 6 に示す。

表 6 CN1 共通バス 各信号の内容

| 番号                                                | 記号                                      | 内容                         | 備考            |

|---------------------------------------------------|-----------------------------------------|----------------------------|---------------|

| A9,A11,A15,A17,A19<br>B5,B8,B12,B20,B23,B31<br>C9 | GND                                     | ディジタルグランド                  |               |

| A31,A32<br>B4,B6,B7,B9,B10,B32<br>C31,C32         | +5V                                     | ディジタル 5V                   |               |

| C10,B3                                            | TRIP1_,TRIP2_                           | トリップ信号                     | Lでトリップ        |

| B11                                               | EMG_                                    | 非常停止                       | Lで停止          |

| B1                                                | PWMRST_                                 | PWM リセット信号<br>(トリップレジスタ解除) | L でリセット       |

| A12,A20                                           | RXD,TXD                                 | 通信用                        |               |

| A1-5                                              | D0-D31                                  | データバス 32bit                |               |

| C1-8,C11,C13-30<br>A23-30<br>B17-19,B21-22,B24-30 | A2-A19                                  | アドレスバス 18bit               |               |

| A22                                               | DIR                                     | 双方向バスバッファ                  | Lで本 FPGA→外部機器 |

| A13                                               | CS1_                                    | チップセレクト信号                  | Lでアクティブ       |

| B2                                                | RD_                                     | リード信号                      | L でアクティブ      |

| C12                                               | RST_                                    | リセット信号                     | L でリセット       |

| A14                                               | WR_                                     | ライト信号                      | L でアクティブ      |

| A16                                               | RDY_                                    | レディ信号                      | L でアクティブ      |

| A18                                               | BBEN_                                   | バスバッファイネーブ<br>ル            | Lでアクティブ       |

| A6,A7<br>A8,A10<br>A21                            | INT1A_,INT1B_<br>INT4A_,INT4B_<br>ADST_ | 割り込み信号                     | L でアクティブ      |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>11/23</sub>

### 3. 2 CN2 PG インターフェース

- (1)コネクタは MR-8RAM とする。

- (2)コネクタマップは表8の通りとする。

- (3)各信号の内容を表9に示す。

表 8 CN2 PG インターフェース コネクタマップ

| 10 10 | / / / / / |

|-------|-----------|

| pin#  | signal    |

| 1     | PGA       |

| 2     | ENV15     |

| 3     | ENM       |

| 4     | ENV15     |

| 5     | PGB       |

| 6     | PGZ       |

| 7     | ENM       |

| 8     | ENV15     |

表 9 CN2 PG インターフェース 各信号の内容

| Pin#  | 記号          | I/O | 内容          | 備考 |

|-------|-------------|-----|-------------|----|

| 1,5,6 | PGA,PGB,PGZ | I   | PG パルス信号    |    |

| 2,4,8 | ENV15       | -   | PG 用 15V 電源 |    |

| 3,7   | ENM         | -   | PG 用グランド    |    |

**Power Electronics Lab.** Nagaoka University of Tech.

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>12/23</sub>

DWG. NO.

Memo:

## 3.3 CN3 PWM 信号インターフェース

(B判)2007/08/01 コネクタマップ修正 阿部

- (1)コネクタは HIF6-40PA-A.27DS とする。

- (2)コネクタマップは表 10 の通りとする。

- (3)各信号の内容は表 11 に示す。

表 10 CN3 PWM 信号インターフェース コネクタマップ

| 2C 10 C113 | 1 44 141   D / J | ///  | ーヘーコイクグマップ |

|------------|------------------|------|------------|

| pin#       | signal           | pin# | signal     |

| A1         | GND              | B1   | GND        |

| A2         | P5               | B2   | P5         |

| A3         | P5               | В3   | P5         |

| A4         | OPOUT2           | B4   | OPOUT1     |

| A5         | RUN              | B5   | DB_        |

| A6         | 73X              | B6   | OPIN       |

| A7         | PWM17            | B7   | PWM16      |

| A8         | GND              | B8   | GND        |

| A9         | P5               | B9   | P5         |

| A10        | PWM15            | B10  | PWM14      |

| A11        | PWM13            | B11  | PWM11      |

| A12        | PWM12            | B12  | PWM10      |

| A13        | PWM9             | B13  | PWM8       |

| A14        | P5               | B14  | P5         |

| A15        | GND              | B15  | GND        |

| A16        | PWM7             | B16  | PWM6       |

| A17        | PWM5             | B17  | PWM3       |

| A18        | PWM4             | B18  | PWM2       |

| A19        | PWM1             | B19  | PWM0       |

| A20        | GND              | B20  | GND        |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

## 表 11 CN3 PWM 信号インターフェース 各信号の内容

| Pin#                | 記号      | I/O | 内容        | 備考               |

|---------------------|---------|-----|-----------|------------------|

| A2,A3,A9,A14        | P5      | -   | 5V 電源     |                  |

| B2,B3,B9,B14        |         |     |           |                  |

| A1,A8,A15,A20       | GND     | _   | デジタルグランド  |                  |

| B1,B8,B15,B20       |         |     |           |                  |

| A7,A10,A11,A12,A13, | PWM0-17 | О   | PWM 信号    | H アクティブ          |

| A16,A17,A18,A19     |         |     |           | (H で IGBT がオン)   |

| B7,B10,B11,B12,B13, |         |     |           |                  |

| B16,B17,B18,B19     |         |     |           |                  |

|                     |         |     |           |                  |

| A6                  | 73X     | О   | 初期充電回路用   | H アクティブ          |

|                     |         |     |           | (H で初期充電抵抗短絡)    |

| A5                  | RUN     | О   | DB 動作許可信号 | H アクティブ          |

|                     |         |     |           | (HでDB動作許可)       |

| A4                  | OPOUT   | О   | オプション出力   |                  |

| B5                  | DB_     | I   | DB 動作信号   | L アクティブ          |

|                     |         |     |           | (LでDB動作(IGBTオン)) |

| B6                  | OPIN    | I   | オプション入力   |                  |

**Power Electronics Lab.**Nagaoka University of Tech.

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

14/23

## 3.4 CN4 検出ボードデジタルインターフェース

- (1)コネクタは MR-34RMA とする。

- (2)コネクタマップは表 12 の通りとする。

- (3)各信号の内容は表 13 に示す

表 12 CN4 検出ボードデジタルインターフェース コネクタマップ

| /火田// |        |

|-------|--------|

| pin#  | signal |

| 1     | GND    |

| 2     | OC1_   |

| 3     | OC2_   |

| 4     | OV1_   |

| 5     | OV2_   |

| 6     | GND    |

| 7     | OCLU_  |

| 8     | OCLV_  |

| 9     | OCLW_  |

| 10    | TRIP1_ |

| 11    | GND    |

| 12    | DSCK   |

| 13    | RH_    |

| 14    | SH_    |

| 15    | TH_    |

| 16    | VR     |

| 17    | VS     |

| 18    | VT     |

|       | GND    |

| 20    | OP2    |

| 21    | THY_   |

| 22    | GND    |

| 23    | RL_    |

| 24    | ST_    |

| 25    | TL_    |

| 26    | OP1    |

| 27    | GND    |

| 28    | IU     |

| 29    | IV     |

| 30    | IW     |

| 31    | GND    |

| 32    | VU     |

| 33    | VV     |

| 34    | VW     |

|       |        |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

## 表 13 CN4 F28DSK I/O Connector 各信号の内容

| Pin#     | 記号                | I/O | 内容          | 備考            |

|----------|-------------------|-----|-------------|---------------|

| 2,3      | OC1_,OC2_         | I   | 過電流信号       | Lアクティブ        |

|          |                   |     |             | (過電流で L)      |

| 4,5      | OV1_,OV2_         | I   | 過電圧信号       | Lアクティブ        |

|          |                   |     |             | (過電圧で L)      |

| 7,8,9    | OCLU_,OCLV_,OCLW_ | I   | 電流制限信号      | Lアクティブ        |

|          |                   |     |             | (制限レベルを超過時 L) |

| 10       | TRIP1_            | О   | トリップ信号      | Lアクティブ        |

|          |                   |     |             | (L でトリップ)     |

| 12       | DSCK              | О   | △Σ変換用クロック   |               |

| 13,14,15 | RH_,SH_,TH_       | I   | 入力電圧最大相信号   | Lアクティブ        |

|          |                   |     |             | (最大相時に L)     |

| 16,17,18 | VR_,VS_,VT_       | I   | 入力電圧極性信号    | Hアクティブ        |

|          |                   |     |             | (極性が正の場合に H)  |

| 20,26    | OP1,OP2           | I   | 予備          |               |

| 21       | THY_              | О   | 初期充電スイッチ用信号 | Lアクティブ        |

|          |                   |     |             | (Lで初期充電抵抗短絡)  |

| 23,24,25 | RL_,SL_,TL_       | I   | 入力電圧最小相信号   | Lアクティブ        |

|          |                   |     |             | (最小相のとき L)    |

| 28,29,30 | IU,IV,IW          | I   | 出力電流極性信号    | H アクティブ       |

| 32,33,34 | VU,VV,VW          | I   | △∑変換用検出信号   |               |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

16/23

## 3.5 CN5 検出ボードアナログインターフェース

- (1)コネクタは MR-20 RAM とする。

- (2)コネクタマップは表 13 の通りとする

- (3)各信号の内容は表 14 に示す。

表 13 CN5 検出ボードアナログインターフェース コネクタマップ

| 男山 小 | トノノロクインダーフェース、 |

|------|----------------|

| pin# | signal         |

| 1    | AGND           |

| 2    | D_IU           |

| 3    | D_IV           |

| 4    | D_IW           |

| 5    | AGND           |

| 6    | D_EDC          |

| 7    | NC             |

| 8    | NC             |

| 9    | AGND           |

| 10   | NC             |

| 11   | AGND           |

| 12   | NC             |

| 13   | AGND           |

| 14   | D_VR           |

| 15   | NC             |

| 16   | D_VT           |

| 17   | AGND           |

| 18   | D_OP1          |

| 19   | AGND           |

| 20   | D_OP2          |

|      |                |

表 14 CN5 検出ボードアナログインターフェース 信号内容

| Pin#  | 記号             | I/O | 内容               | 備考 |

|-------|----------------|-----|------------------|----|

| 2,3,4 | D_IU,D_IV,D_IW | I   | 出力電流検出値(U,V,W 相) |    |

| 6     | D_EDC          | Ι   | 直流中間電圧検出値        |    |

| 14,16 | D_VR,D_VT      | Ι   | 入力電圧検出値(R,T 相)   |    |

| 18,20 | D_OP1,D_OP2    | I   | 予備               |    |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

表 15 AD コンバータ割付表

|          |       | . ,   |          |

|----------|-------|-------|----------|

| AD コンバータ | チャンネル | 信号名   | 内容       |

|          | CH1   | D_VR  | 入力 R 相電圧 |

| 1        | CH2   | D_VT  | 入力T相電圧   |

| 1        | СНЗ   | D_OP1 | オプション    |

|          | CH4   | D_OP2 | オプション    |

| 2        | CH1   | D_IU  | 出力U相電流   |

|          | CH2   | D_IV  | 出力 V 相電流 |

|          | СНЗ   | D_IW  | 出力W相電流   |

|          | CH4   | D_EDC | 直流中間電圧   |

#### 3.6 電源入力

#### 3. 6. 1 CN6 5V 電源

- (1)コネクタは B2PS-VH とする。

- (2)コネクタマップは表 15 の通りとする

表 15 CN6 5V 電源 コネクタマップ

| 20 0 | 1106.100 |

|------|----------|

| pin# | signal   |

| 1    | P5       |

| 2    | GND      |

### 3. 6. 2 CN7 ±15V 電源

- (1)コネクタは B3PS-VH とする。

- (2)コネクタマップは表 16,表 17 の通りとする

表 16 CN7A 15V 電源 コネクタマップ

| pin# | signal |

|------|--------|

| 1    | P15    |

| 2    | AGND   |

| 3    | N15    |

表 17 CN7B 15V 電源 コネクタマップ

| pin# |   | signal |

|------|---|--------|

|      | 1 | P15    |

|      | 2 | AGND   |

|      | 3 | N15    |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech    |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

18/23

### 3.7 FPGA フラッシュライタインターフェース

#### 3. 7. 1 CN8

(1)コネクタは FX2-20P-1.27DS とする。

(2)コネクタマップは表 18 の通りとする

表 19 CN8 FPGA フラッシュライタ コネクタマップ

| ピン番号 | 機能   | ピン番号 | 機能    |

|------|------|------|-------|

| A1   | VDPP | B1   | VPP   |

| A2   | VDPP | B2   | VPN   |

| A3   | GND  | В3   | GND   |

| A4   | GND  | B4   | GND   |

| A5   | TCK  | B5   | TDO   |

| A6   | TDI  | B6   | TMS   |

| A7   | GND  | В7   | RCK   |

| A8   | GND  | B8   | TRSTB |

| A9   | GND  | В9   | VDD   |

| A10  | GND  | B10  | VDD   |

#### 3. 7. 2 CN9

(1)コネクタは FTSH-113-01-L-D-K とする。

(2)コネクタマップは表 20 の通りとする。

表 20 CN9 FPGA フラッシュライタ コネクタマップ

| ピン番号  | 機能     | ピン番号 | 機能     |

|-------|--------|------|--------|

| しノ 併写 | 17戌 月已 | レノ俄写 | 17或 月已 |

| 25    | NC     | 26   | VDD    |

| 23    | NC     | 24   | VDDP   |

| 21    | NC     | 22   | TRSTB  |

| 19    | GND    | 20   | RCK    |

| 17    | GND    | 18   | TMS    |

| 15    | NC     | 16   | TDO    |

| 13    | NC     | 14   | TDI    |

| 11    | GND    | 12   | TCK    |

| 9     | GND    | 10   | GND    |

| 7     | GND    | 8    | VPN    |

| 5     | NC     | 6    | VPP    |

| 3     | NC     | 4    | VDDP   |

| 1     | NC     | 2    | VDDP   |

**Power Electronics Lab.** Nagaoka University of Tech.

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G

DWG. NO.

Memo:

## 4. 付録 (2007/09/11 追加 阿部)

## 4.1 FPGA ピン配置

表 1 FPGAピン配置\_1

| nin No | APA300機能 | Aヒン配直_I       | 信品专向 |

|--------|----------|---------------|------|

| pin No |          | signal<br>GND | 信号方向 |

| 1      | GND      |               | 7    |

| 2      | I/O      | A0            | I    |

| 3      | I/O      | A1            | I    |

| 4      | 1/0      | A2            | I    |

| 5      | I/O      | A3            | I    |

| 6      | I/O      | A4            | I    |

| 7      | I/O      | A5            | I    |

| 8      | I/O      | A6            | I    |

| 9      | I/O      | A7            | I    |

| 10     | I/O      | A8            | I    |

| 11     | I/O      | A9            | I    |

| 12     | I/O      | A10           | I    |

| 13     | I/O      | A11           | I    |

| 14     | I/O      | A12           | I    |

| 15     | I/O      | A13           | I    |

| 16     | VDD      | VDD           |      |

| 17     | GND      | GND           |      |

| 18     | I/O      | A14           | I    |

| 19     | I/O      | A15           | I    |

| 20     | I/O      | A16           | I    |

| 21     | I/O      | A17           | I    |

| 22     | VDDP     | VDDP          |      |

| 23     | I/O      | TP01          |      |

| 24     | I/O      | RST_          | I    |

| 25     | AGND1    | AGND1         |      |

| 26     | NPECL    | NPECL         |      |

| 27     | AVDD1    | AVDD1         |      |

| 28     | PPECL    | PPECL         |      |

| 29     | GND      | GND           |      |

| 30     | I/O      | RWMRST_       | I    |

| 31     | I/O      | A18           | I    |

| 32     | I/O      | A19           | I    |

| 33     | I/O      | D15           | I/O  |

| 34     | I/O      | D14           | I/O  |

| 35     | I/O      | D13           | I/O  |

| 36     | VDD      | VDD           |      |

| 37     | I/O      | D12           | I/O  |

| 38     | I/O      | D11           | I/O  |

| 39     | I/O      | D10           | I/O  |

| 40     | VDDP     | VDDP          |      |

| 41     | GND      | GND           |      |

| 42     | I/O      | D9            | I/O  |

| 43     | I/O      | D8            | I/O  |

| 44     | I/O      | D7            | I/O  |

| 45     | I/O      | D6            | I/O  |

| 46     | I/O      | D5            | I/O  |

| 47     | I/O      | D4            | I/O  |

| 48     | I/O      | D3            | I/O  |

| 49     | I/O      | D2            | I/O  |

| 50     | I/O      | D1            | I/O  |

| 51     | I/O      | D0            | I/O  |

| 01     | ., 0     |               | ., 0 |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>20/23</sub>

| 表 2 FPGAピン配置_ | 2 |

|---------------|---|

|---------------|---|

| Г      |          | Aピン配置_2 |      |

|--------|----------|---------|------|

| pin No | APA300機能 | signal  | 信号方向 |

| 53     | VDDP     | VDDP    |      |

| 54     | I/O      | TRIP1_  | I    |

| 55     | I/O      | TRIP2_  | I    |

| 56     | I/O      | EMG_    | I    |

| 57     | I/O      | ADINT   | 0    |

| 58     | I/O      | INT4B_  | 0    |

| 59     | I/O      | INT4A_  | 0    |

| 60     | I/O      | INT1B_  | 0    |

| 61     | I/O      | INT1A_  | 0    |

| 62     | I/O      | RD_     | I    |

| 63     | I/O      | WR_     | I    |

| 64     | I/O      | CS_     | I    |

| 65     | GND      | GND     |      |

| 66     | I/O      | RDY     | I    |

| 67     | I/O      | BBEN_   | I    |

| 68     | I/O      | DIR_    | I    |

| 69     | I/O      | RXD     | I    |

| 70     | I/O      | TXD     | I    |

| 71     | VDD      | VDD     |      |

| 72     | VDDP     | VDDP    |      |

| 73     | I/O      | ADST1_  | 0    |

| 74     | I/O      | ADRD1_  | 0    |

| 75     | I/O      | BUSY1   | I    |

| 76     | I/O      | ADST2_  | 0    |

| 77     | I/O      | ADRD2_  | 0    |

| 78     | I/O      | BUSY2   | I    |

| 79     | I/O      | TP02    |      |

| 80     | I/O      | TP03    |      |

| 81     | GND      | GND     |      |

| 82     | I/O      | DSCK    | 0    |

| 83     | I/O      | VW      | I    |

| 84     | I/O      | VV      | I    |

| 85     | I/O      | VU      | I    |

| 86     | I/O      | THY_    | 0    |

| 87     | I/O      | TP04    |      |

| 88     | VDD      | VDD     |      |

| 89     | VDDP     | VDDP    |      |

| 90     | I/O      | OP2     | I    |

| 91     | I/O      | OCLW_   | I    |

| 92     | I/O      | OCLV_   | I    |

| 93     | I/O      | OCLU_   | I    |

| 94     | I/O      | IW      | I    |

| 95     | I/O      | IV      | I    |

| 96     | I/O      | IU      | I    |

| 97     | GND      | GND     |      |

| 98     | I/O      | VT      | I    |

| 99     | I/O      | VS      | I    |

| 100    | I/O      | VR      | I    |

| 101    | TCK      | TCK     |      |

| 102    | TDI      | TDI     |      |

| 103    | TMS      | TMS     |      |

| 104    | VDDP     | VDDP    |      |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>21/23</sub>

| 双 3 FruA L / ILIE 3 | 表 3 | <b>FPGA</b> | ピン配置 | 3 |

|---------------------|-----|-------------|------|---|

|---------------------|-----|-------------|------|---|

|        |              | A E ン配直_3 | <i></i> |

|--------|--------------|-----------|---------|

| pin No | APA300機能     | signal    | 信号方向    |

| 105    | \ (DD        | GND       |         |

| 106    | VPP          | VPP       |         |

| 107    | VPN          | VPN       |         |

| 108    | TDO          | TDO       |         |

| 109    | TRST         | TRSTB     |         |

| 110    | RCK          | RCK       |         |

| 111    | I/O          | OV2_      | I       |

| 112    | I/O          | OV1_      | I       |

| 113    | I/O          | OC2_      | I       |

| 114    | I/O          | OC1_      | I       |

| 115    | I/O          | OP1_      | I       |

| 116    | I/O          | TL_       | I       |

| 117    | I/O          | SL_       | I       |

| 118    | I/O          | RL_       | I       |

| 119    | I/O          | TH_       | I       |

| 120    | I/O          | SH_       | I       |

| 121    | I/O          | RH_       | I       |

| 122    | GND          | GND       |         |

| 123    | 3.3V         | VDDP      |         |

| 124    | I/O          | TP05      |         |

| 125    | I/O          | TP06      |         |

| 126    | VDD          | VDD       |         |

| 127    | I/O          | TP07      |         |

| 128    | I/O          | CLK20M    | I       |

| 129    | PPECL2/Input | PPECL     |         |

| 130    | GND          | GND       |         |

| 131    | AVDD         | AVDD2     |         |

| 132    | NPECL2       | NPECL2    |         |

| 133    | AGND         | AGND      |         |

| 134    | GL           | GL        |         |

| 135    | I/O          | PWM0      | 0       |

| 136    | I/O          | PWM1      | 0       |

| 137    | I/O          | PWM2      | 0       |

| 138    | VDDP         | VDDP      |         |

| 139    | I/O          | PWM3      | 0       |

| 140    | I/O          | PWM4      | 0       |

| 141    | GND          | GND       |         |

| 142    | VDD          | VDD       |         |

| 143    | I/O          | PWM5      | 0       |

| 144    | I/O          | PWM6      | 0       |

| 145    | I/O          | PWM7      | 0       |

| 146    | I/O          | PWM8      | 0       |

| 147    | I/O          | PWM9      | 0       |

| 148    | I/O          | PWM10     | 0       |

| 149    | I/O          | PWM11     | 0       |

| 150    | I/O          | PWM12     | 0       |

| 151    | I/O          | PWM13     | 0       |

| 152    | I/O          | PWM14     | 0       |

| 153    | I/O          | PWM15     | 0       |

| 154    | I/O          | PWM16     | 0       |

| 155    | I/O          | PWM17     | 0       |

| 156    | GND          | GND       | 3       |

| 100    | GIND         | GND       |         |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>22/23</sub>

| 表 4 FPGAピン配置_4 | 表 4 | FPGA | ピン配置 | 4 |

|----------------|-----|------|------|---|

|----------------|-----|------|------|---|

| NI            | APA300機能 | A ビン配直_4    | 后日士白 |

|---------------|----------|-------------|------|

| pin No<br>157 | VDDP     | signal VDDP | 信号方向 |

|               |          |             | 0    |

| 158           | I/O      | BOFF1       | 0    |

| 159           | I/O      | BOFF2       | 0    |

| 160           | I/O      | BOFF3       | 0    |

| 161           | I/O      | BOFF4       | 0    |

| 162           | GND      | GND         | •    |

| 163           | 1/0      | 73X         | 0    |

| 164           | I/O      | RUN         | 0    |

| 165           | I/O      | OPOUT2      | 0    |

| 166           | I/O      | DB_         | I    |

| 167           | I/O      | OPIN        | I    |

| 168           | I/O      | OUTPUT1     | 0    |

| 169           | I/O      | PGZ         | I    |

| 170           | VDDP     | VDDP        |      |

| 171           | VDD      | VDD         |      |

| 172           | I/O      | PGB         | I    |

| 173           | I/O      | PGA         | I    |

| 174           | I/O      | LED4        | 0    |

| 175           | I/O      | LED3        | 0    |

| 176           | I/O      | LED2        | 0    |

| 177           | I/O      | LED1        | 0    |

| 178           | GND      | GND         |      |

| 179           | I/O      | TP08        |      |

| 180           | I/O      | TP09        |      |

| 181           | I/O      | TP10        |      |

| 182           | I/O      | TP11        |      |

| 183           | I/O      | TP12        |      |

| 184           | I/O      | TP13        |      |

| 185           | I/O      | OP19        |      |

| 186           | VDDP     | VDDP        |      |

| 187           | VDD      | VDD         |      |

| 188           | I/O      | OP18        |      |

| 189           | I/O      | OP17        |      |

| 190           | I/O      | OP16        |      |

| 191           | I/O      | OP15        |      |

| 192           | I/O      | OP14        |      |

| 193           | I/O      | OP13        |      |

| 194           | I/O      | OP12        |      |

| 195           | GND      | GND         |      |

| 196           | I/O      | OP11        |      |

| 197           | I/O      | OP10        |      |

| 198           | I/O      | OP09        |      |

| 199           | I/O      | OP08        |      |

| 200           | I/O      | OP07        |      |

| 201           | I/O      | OP06        |      |

| 202           | I/O      | OP05        |      |

| 203           | I/O      | OP04        |      |

| 204           | I/O      | OP03        |      |

| 205           | I/O      | OP02        |      |

| 206           | I/O      | OP01        |      |

| 207           | I/O      | OP00        |      |

| 208           | VDDP     | VDDP        |      |

| 200           | V D D F  | V DDF       |      |

| <b>Power Electronics Lab.</b> |

|-------------------------------|

| Nagaoka University of Tech.   |

|       | DATE       | NAME |

|-------|------------|------|

| DRAWN | 11/29/2010 | 佐藤   |

| CHECK |            |      |

PZ06-5058G <sub>23/23</sub>